Co-evolution of algorithms, compilers, and hardware for performance

A Fastcode workshop at PPoPP-26

I have enjoyed working recently with J Nelson Amaral and Yihan Sun to co-organize the upcoming CACHP workshop on the co-evolution of algorithms, compilers, and hardware for performance.

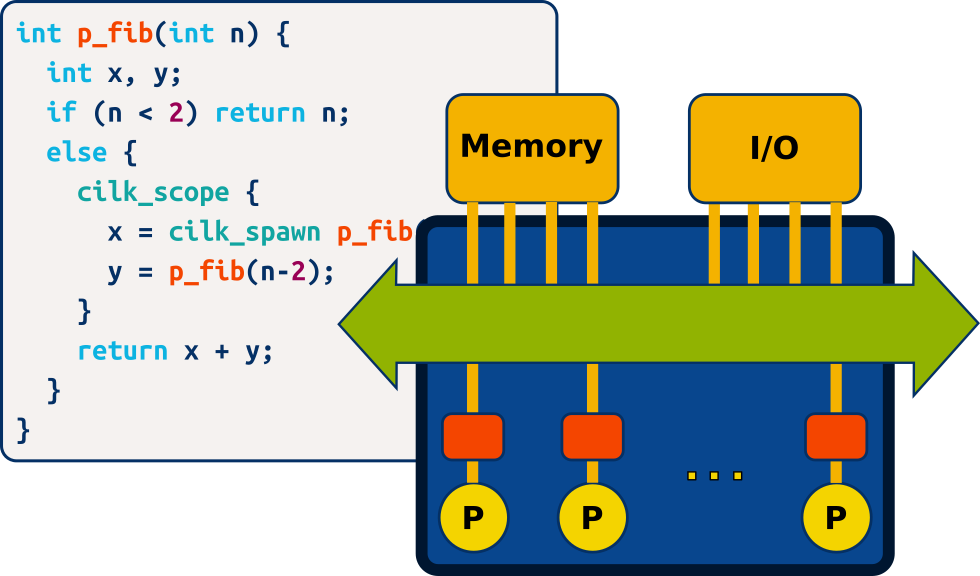

The workshop was born almost one year ago, when Charles Leiserson gave a plenary talk at PPoPP, “Why every CS department should teach software performance engineering.” During the Q&A, Nelson raised his hand and asked how the compilers community could be part of the performance-engineering story. The CACHP webpage now presents a vision for exactly that:

Achieving performance requires advances not only in algorithm design but also in programming models, software construction, compilers, and hardware. Progress in one of these areas often influences and reshapes the others. For example, a new code pattern may first appear as a hand-crafted optimization by an expert programmer, then evolve into a portable compiler transformation, and eventually inspire changes in hardware architecture or system design. Such cross-pollination drives innovation, yet opportunities for the communities to engage in joint discussion remain limited. CACHP aims to bring together researchers and practitioners to explore this co-evolution of algorithms, compilers, and hardware.

Four contributed talks have been accepted for CACHP-26:

Efficient Hardware Primitives for Immediate Memory Reclamation in Optimistic Data Structures (By A. Singh, T. Brown, and M. Spear)

Adaptive Loop Unrolling for Automatic Parallelism Management (By S.V. Satish and S. Westrick)

Synthesizing Dist-Memory Mappings for Tensor Computations with Domain and Hardware Knowledge (By M. Kong)

Co-Design for Performance and Energy-Efficiency in modern AI paradigms (By G. Cong)

Would you like to join the co-evolution? Fastcode is here to help!